SystemVerilog is a powerful hardware description and verification language, extending Verilog’s capabilities. Numerous tutorials and examples are available for beginners, aiding in rapid skill development.

It’s a superset of Verilog, meaning existing Verilog code is generally valid SystemVerilog code, simplifying the transition for experienced designers.

Learning SystemVerilog unlocks advanced features for complex digital design and robust verification, crucial for modern hardware engineering projects.

What is SystemVerilog?

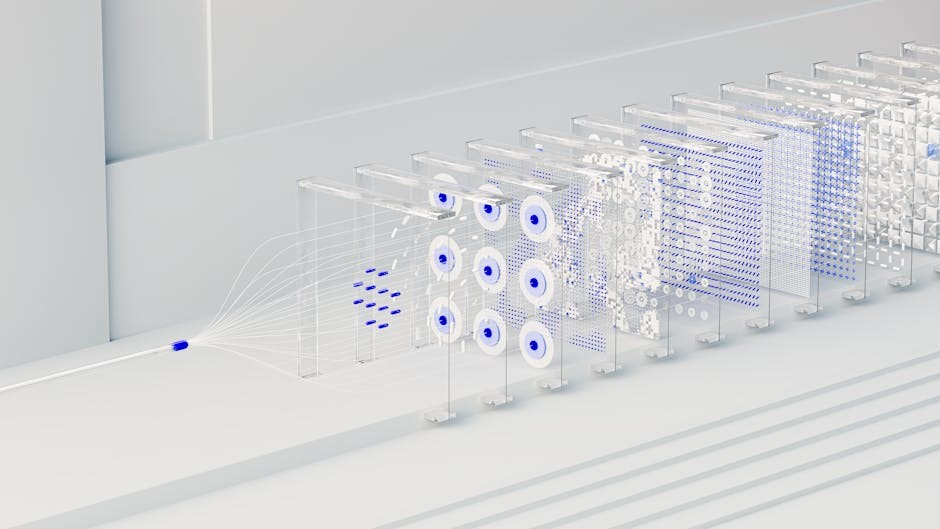

SystemVerilog represents a significant advancement in hardware description languages (HDLs), evolving from its Verilog foundation. It’s not merely an updated version; it’s a comprehensive language suite designed for both verification and design. This includes features for modeling, simulation, and formal verification, making it invaluable for complex systems.

Essentially, SystemVerilog combines the best aspects of Verilog with powerful new capabilities like classes, constrained-random stimulus generation, and advanced assertion techniques. Numerous online tutorials cater to beginners, offering practical examples to grasp these concepts. It’s widely used in the industry for creating robust and reliable hardware designs, and mastering it is a key skill for any digital engineer.

The language’s versatility allows for efficient modeling at various abstraction levels.

SystemVerilog vs. Verilog

While SystemVerilog builds upon Verilog, the differences are substantial. Verilog primarily focuses on hardware description, whereas SystemVerilog expands this to include robust verification capabilities. Key additions include object-oriented programming (OOP) with classes, enhancing code reusability and organization.

Furthermore, SystemVerilog introduces constrained-random stimulus generation, allowing for more thorough and efficient testing compared to Verilog’s manual stimulus creation. Assertions, a crucial part of formal verification, are significantly improved in SystemVerilog. Many tutorials highlight these distinctions, providing examples for comparison.

Essentially, Verilog is a subset of SystemVerilog; all valid Verilog code is also valid SystemVerilog code, but the reverse isn’t true. This makes the transition easier for those familiar with Verilog.

Why Learn SystemVerilog?

SystemVerilog is rapidly becoming the industry standard for hardware design and verification. Mastering it significantly enhances career prospects in the semiconductor industry. Numerous tutorials cater to all skill levels, making learning accessible. Its advanced features, like OOP and constrained-random verification, drastically improve design quality and reduce time-to-market.

Compared to Verilog, SystemVerilog enables more complex designs to be modeled and verified efficiently. The availability of comprehensive examples and a strong community support network further facilitates the learning process. It’s essential for tackling modern hardware challenges.

Ultimately, investing in SystemVerilog skills is an investment in a future-proof career in digital design.

Data Types in SystemVerilog

SystemVerilog offers rich data types – logic, int, and real – alongside fixed and associative arrays. Tutorials demonstrate their usage in modeling hardware.

Basic Data Types (logic, int, real)

SystemVerilog introduces fundamental data types essential for hardware modeling. The logic type represents single-bit values, ideal for digital signals, and can have four states (0, 1, X, Z). int represents signed integers, offering various sizes like 32-bit or 64-bit, depending on the specific implementation and system requirements.

The real type handles floating-point numbers, crucial for analog or mixed-signal simulations. These basic types form the building blocks for more complex data structures. Tutorials often begin with these, illustrating their declaration and assignment. Understanding these types is paramount for accurately representing hardware behavior in your designs. Proper type selection impacts simulation speed and accuracy, so careful consideration is vital.

These data types are foundational for all SystemVerilog designs, and mastering them is the first step in becoming proficient with the language.

Fixed-Size Arrays

SystemVerilog’s fixed-size arrays are collections of elements of the same data type, declared with a specific size at compile time. For example, logic [7:0] my_byte; creates an 8-bit array. These arrays are incredibly useful for representing buses, registers, and memory locations within a hardware design.

Accessing elements is done using indices within the defined range. Tutorials demonstrate how to iterate through these arrays using loops, performing operations on each element. Fixed-size arrays offer efficient memory usage and predictable performance. They are a core component of modeling hardware structures;

Understanding array indexing and manipulation is crucial for effective SystemVerilog coding. They are fundamental for representing and processing data in digital systems.

Associative Arrays

SystemVerilog’s associative arrays, also known as dictionaries, are dynamic data structures that map keys to values. Unlike fixed-size arrays, they don’t require pre-defined indices. You define a key-value pair relationship, allowing flexible data storage and retrieval. For instance, int my_map[string]; creates a map where strings are keys and integers are values.

Tutorials highlight their usefulness in modeling complex relationships, like address decoding or state machines. Accessing elements uses the key, offering a convenient way to manage data without knowing the index beforehand. Associative arrays are powerful for verification, enabling efficient tracking of simulation data.

They provide a dynamic and adaptable approach to data management in hardware description and verification.

Operators and Expressions

SystemVerilog supports arithmetic, logical, and bitwise operators. Mastering these is crucial for constructing expressions and performing calculations within your hardware designs and tutorials.

Arithmetic Operators

SystemVerilog provides a comprehensive set of arithmetic operators for performing mathematical operations on numerical data types like int and real. These operators include addition (+), subtraction (-), multiplication (), division (/), and modulus (%). Understanding their precedence and associativity is vital for accurate expression evaluation.

For instance, a + b c will be evaluated as a + (b * c) due to multiplication’s higher precedence. The modulus operator (%) returns the remainder of a division, useful for implementing counters or generating repeating patterns. When dealing with integer division, SystemVerilog truncates the result towards zero. Careful consideration of data types is essential to avoid unexpected results or overflow errors during arithmetic operations, especially when following a tutorial.

Logical Operators

SystemVerilog employs logical operators to evaluate Boolean expressions, resulting in either 1 (true) or 0 (false). The fundamental logical operators are AND (&&), OR (||), and NOT (!). These operators are crucial for implementing conditional statements and complex decision-making logic within hardware designs.

Short-circuit evaluation is a key feature; for example, in a && b, if a is 0, b is not evaluated. Logical operators differ from bitwise operators, which operate on individual bits. Mastering these operators is essential when following a SystemVerilog tutorial, as they form the basis of control flow and verification constructs. Proper use ensures correct and efficient hardware behavior.

Bitwise Operators

SystemVerilog utilizes bitwise operators to manipulate individual bits within a variable. These operators include AND (&), OR (|), XOR (^), and NOT (~). Unlike logical operators, bitwise operators perform operations on each corresponding bit of their operands, producing a bit-level result. Left shift (<<) and right shift (>>) operators are also vital for bit manipulation.

A SystemVerilog tutorial will emphasize the distinction between logical and bitwise operations. Bitwise operators are frequently used in low-level hardware control, data packing, and unpacking, and implementing efficient algorithms. Understanding these operators is crucial for tasks like setting or clearing specific flags within a register or performing bitfield operations.

Control Flow Statements

SystemVerilog offers if-else statements, for loops, and while loops for controlling program execution. These structures are fundamental for creating dynamic hardware descriptions.

if-else Statements

SystemVerilog’s if-else statements provide conditional execution, crucial for modeling complex digital logic. The basic structure involves an if keyword, followed by a condition enclosed in parentheses. If the condition evaluates to true, the code block immediately following the if statement is executed.

An optional else block can be included; this block executes only if the if condition is false. Nested if-else statements are also permitted, allowing for multiple conditional branches. Proper indentation enhances readability. For example:

if (condition) begin

// Code to execute if condition is true

end else begin

// Code to execute if condition is false

end

These statements are essential for implementing decision-making processes within hardware designs.

for Loops

SystemVerilog for loops enable repetitive execution of code blocks, streamlining tasks like array processing and signal manipulation. A standard for loop consists of three parts: initialization, condition, and increment/decrement. The initialization statement executes once at the beginning, setting the loop counter.

The condition is checked before each iteration; the loop continues as long as the condition remains true. Finally, the increment/decrement statement updates the loop counter after each iteration. Here’s a basic example:

for (int i = 0; i < 10; i++) begin

// Code to be executed repeatedly

end

These loops are fundamental for iterating through data structures and performing operations on multiple elements efficiently within hardware descriptions.

while Loops

SystemVerilog while loops provide a mechanism for repeatedly executing a block of code as long as a specified condition remains true. Unlike for loops, while loops don’t require pre-defined initialization or increment steps; these are handled within the loop body itself.

The loop continues executing as long as the condition evaluates to true. It’s crucial to ensure the condition eventually becomes false to avoid infinite loops. A basic structure looks like this:

while (condition) begin

// Code to be executed repeatedly

// Update variables to affect the condition

end

while loops are particularly useful when the number of iterations isn’t known beforehand, making them ideal for event-driven simulations and control logic.

Modules and Instantiation

SystemVerilog designs are built using modules, encapsulating logic. Module instantiation allows reusing these building blocks, creating complex hierarchies for efficient hardware description.

Module Definition

SystemVerilog modules are the fundamental building blocks of any design. Defining a module involves specifying its name, input and output ports, and the internal logic that implements its functionality. The basic syntax begins with the keyword module followed by the module name and a port list enclosed in parentheses.

Within the module, you declare signals (wires and registers) to represent data and implement the desired logic using continuous assignments or behavioral blocks. These blocks describe how the outputs respond to changes in inputs. A module definition always concludes with the keyword endmodule.

Proper module definition is crucial for creating reusable and maintainable hardware designs. Understanding port declarations and signal types is essential for effective SystemVerilog coding.

Port Declaration

SystemVerilog port declarations define the interface between a module and its environment. Ports specify the inputs and outputs that allow data to flow in and out of the module. They are declared within the module’s parentheses following the module name. Each port has a direction (input, output, or inout) and a data type, such as logic, int, or real.

Ports can also have widths specified for arrays. Using clear and descriptive port names is vital for readability. Proper port declaration ensures correct connectivity during module instantiation and simulation.

Understanding port directionality and data types is fundamental to building interconnected and functional SystemVerilog designs. Careful port definition prevents errors and simplifies debugging.

Module Instantiation

SystemVerilog module instantiation creates instances of pre-defined modules within a larger design. This process involves specifying the module name, instance name, and connecting the module’s ports to signals in the current module. The instance name uniquely identifies the module within the hierarchy.

Port connections are made using the .port_name(signal_name) syntax, mapping the module’s ports to corresponding signals. Correct port mapping is crucial for proper functionality.

Module instantiation allows for code reuse and hierarchical design, simplifying complex systems. Understanding instantiation is key to building scalable and maintainable SystemVerilog projects.

Testbenches and Simulation

SystemVerilog testbenches verify designs through stimulus generation, assertions, and signal monitoring. Simulation tools analyze behavior, ensuring correct functionality before hardware implementation.

Stimulus Generation

Stimulus generation within SystemVerilog testbenches is crucial for comprehensively verifying a design’s functionality. It involves creating input patterns that exercise all possible scenarios and corner cases. This is often achieved using procedural blocks, tasks, and functions to define sequences of signals.

Random stimulus generation is a powerful technique, employing constrained-randomization to create diverse and unpredictable inputs. This helps uncover subtle bugs that deterministic tests might miss. Furthermore, techniques like directed tests, where specific input sequences are crafted to target particular functionalities, are also commonly used.

Effective stimulus generation requires careful planning and consideration of the design’s specifications. The goal is to create a test environment that thoroughly validates the design’s behavior under various operating conditions, ensuring its reliability and correctness.

Verification with Assertions

Verification with assertions in SystemVerilog significantly enhances the reliability of hardware designs. Assertions are statements that specify expected behavior, allowing for dynamic checking during simulation. They act as self-checking code, immediately flagging violations of design intent.

SystemVerilog provides a powerful assertion language, enabling the creation of both immediate and concurrent assertions. Immediate assertions are evaluated synchronously, while concurrent assertions run in parallel with the design, offering real-time monitoring. Utilizing assertions helps catch bugs early in the design cycle, reducing debugging time and costs.

Assertions are integral to formal verification, providing a means to prove design correctness mathematically. They are a cornerstone of modern verification methodologies, improving design quality and confidence.

Displaying Signals

Displaying signals in SystemVerilog is crucial for debugging and understanding design behavior during simulation. The `$display` system task is fundamental, allowing you to print values of variables and custom messages to the console. Formatting options within `$display` control the output’s appearance, enhancing readability.

For more complex monitoring, `$monitor` continuously displays signal values whenever they change, providing a dynamic view of the simulation. SystemVerilog also offers `$strobe`, which displays signals only on specific clock edges, useful for synchronous designs. These tasks are essential for tracing signal transitions and identifying potential issues.

Waveform viewers, integrated with simulators, provide a graphical representation of signals over time, offering a comprehensive visualization of design activity.

Leave a Reply

You must be logged in to post a comment.